# PROVIDE HOLISTIC DEVELOPMENT THROUGH PROJECT-BASED LEARNING IN ENGINEERING MODULES

#### Linus Low Koon Teck Ngee Ann Polytechnic

## ABSTRACT

In traditional engineering education, it is common to find lessons being dominated by hour-long lectures during which most, if not all of the materials prepared for the module are being dispensed in a transmittal mode with little active participation from students. It is also typical to find these lessons designed primarily for the development of technical knowledge and skills with little focus on the personal and interpersonal skills development of the student. Much education research has shown that this approach is inadequate to prepare our graduates with expertise in their field of qualification as well as with highly developed interpersonal, personal and transferable professional skills attributes. A change is required. This paper presents how a change in lesson design adopted by "IC Layout", a module offered under the Electronics and Computer Engineering Diploma of Ngee Ann Polytechnic, addresses some of the concerns mentioned above. The key change involved the incorporation of project-based learning where students assume the role of IC layout engineers working in a team to build a layout of a Linear Feedback Shift Register. In this project-based learning experience, students identify their knowledge gaps in cell layout methodologies and perform background research to fill those gaps, they apply knowledge gained to build and verify their layouts according to design rules. As a final deliverable, students will have to communicate their best layout by presenting justifications on why their layout is the best. This lesson design also aims to simulate a real working environment by exposing students to technologies and experiences of a real work place with the use of platforms such as wiki where students share and review information posted by other team members, co-author documents that explains the concepts of cell layout methodologies, evaluate and critique the product of other members, and collaboratively builds on each others work to present the final product. These experiences have increased the level of students' engagement in learning. They tend to show greater interest in the topics and demonstrated a deeper understanding in the concepts and theories related to this module.

#### **KEYWORDS**

Project-based learning, experiential learning, learning design

#### INTRODUCTION

Project-based learning is not something new. William H Kilpatrick published paper "The Project Method" in 1918 systematically explained and rationalized project-based learning [1].

The project approach is enticing because it offers the student more control of the learning process resulting in higher student involvement and motivation. The degree of freedom granted to the student in the learning process depends on the type of project based approach used. In

open ended or unstructured projects, students are given guidelines and little structure to encourage risk taking and innovative thinking. On the other end, structured projects are characterized by the many constraints or limitations placed by the instructor. These constraints may include product specifications and functions, methodologies used or specific sources of information. Somewhere in-between these extremes are the semi-structured and real-life projects [2]. The project can be topic-related or genre-related.

The process used in project-based learning typically consists of the following activities: (a) project definition (b) investigation (c) processing of data (d) realization and (e) evaluation. The degree of freedom given to students in each of these activities will depend on the type of project-based learning approach used by the instructor. The requirements of the project is first clarified and understood. During the investigation phase, activities will include finding resources, collecting data, interviewing, observations and selecting the appropriate data. In the processing activities phase, the student tries to make sense of the data collected through analysis, classifying and synthesis. In the realization phase, students will conceptualize possible solutions, learn how to prioritize and manage their time and produce a prototype or model. Evaluation of the project could be done individually or in groups through presentations, reports, self-reflection, peer and self-assessment [1][3].

Assessment of the project could be either summative or formative or both. The summative assessment would be used to evaluate the final outcome of the project. It could be based on reports, presentation or viva. The formative assessment could be use to evaluate the students work as they progress through the project. By pacing the deadlines of the formative assessments, the progress of the students can be monitored and timely feedback can be given to the students. This forces them to start work early and prevents them from producing a rush job near the project deadline [2].

The project based learning approach demands a lot of time and effort from both student and teacher. Another concern is the degree of subjectivity in the assessment in project-based learning. However with properly designed assessment rubrics and team assessment, the degree of subjectivity can be reduced.

## USE OF TECHNOLOGY IN PROJECT-BASED LEARNING

Project-based learning can leverage on Web 2.0 applications to make the process more efficient, visible and collaborative. The Web 2.0 applications can support the following areas in project-based learning: student collaboration, collection of data and information, organizing data, contacting experts, producing artifacts, constructing content, self-reflection, peer-review of learning content, ongoing feedback [4].

Table 1 shows some of the Web 2.0 learning activities that can be used to support projectbased learning.

| Learning Activity | Web 2.0 Technology | Examples of Web 2.0 tools |

|-------------------|--------------------|---------------------------|

| Online Resources  | Search engines     | http://www.google.com.sg  |

|                   | Web feeds          | http://news.bbc.co.uk     |

| Table 1                                                     |

|-------------------------------------------------------------|

| Sample of Web 2.0 Tools for Use With Project-Based Learning |

| Constructing Content | Wikis       | http://www.wikispaces.com   |

|----------------------|-------------|-----------------------------|

|                      | Vidcast     | http://www.teachertube.com/ |

|                      | Podcasts    | http://www.podomatic.com/   |

|                      | Photographs | http://www.flickr.com       |

|                      | Mindmapping | http://bubbl.us/edit.php    |

|                      | Maps        | http://maps.google.com      |

| Reflection           | Blogging    | http://www.blogger.com/     |

The internet has made searches for information more effective and efficient. Many search engines are available out on the web. Also information can be pushed to the student's desktop using RSS feeds. However, the student must learn to be critical of the data presented on the internet and verify the authenticity of the information.

Students could collaboratively construct the content using either text using wikis or document sharing web sites; or diagrams using mind maps and concept maps; or using photographs or videos.

The students' progress in the project can be monitored by asking the students to reflect on their learning journey in their blogs.

## APPLICATION OF PROJECT-BASED LEARNING TO INTEGRATED CIRCUIT LAYOUT

#### Context

The students taking the Integrated Circuit Layout (ICL) module are final-year students doing a 3year Electronic and Computer Engineering Diploma course offered by Ngee Ann Polytechnic, Singapore.

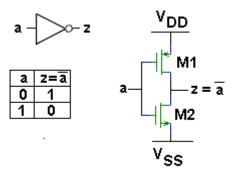

The students would have done some digital integrated circuit layout (or IC Layout) in their second year module, Microchip Technology (MCTE). They would have learnt how to layout primitive digital cells like the inverter logic gate (Figure 1).

Figure 1: CMOS inverter logic gate.

Figure 2: Layout of a CMOS inverter gate.

In a very brief summary, computer functions are carried out by logic gates like the one in Figure 1. Some logic gates are more complex than others. However, all logic gates would be made up of two or more transistors connected together to form the logic function. The transistor is formed by patterning different process layers on a semiconductor wafer using photolithography. The patterns are drawn manually on a PC using some IC Layout editing software. Figure 2 shows the layout of a CMOS inverter gate.

Students taking the ICL module would scaffold on their MCTE IC layout knowledge to learn about IC layout methodologies to layout more complex circuits and subsystems. They are also introduced to industry based IC layout design rules which are meant to ensure that the structures patterned are reproducible consistently on the microchip. These topics form about 30% of the module. Previously, these topics could be covered in 10 hours using the traditional lecture/ tutorial/ lab approach. However, because a major portion of these topics involves rules and methodologies, the students find the lectures too abstract and uninteresting.

Hence the project-based approach was tried.

## Requirements

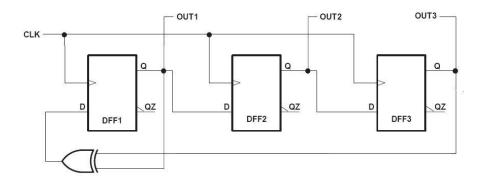

The structured project approach was adopted due to the limited time allocated for these topics. The students were grouped into teams of 3-5 students. The groups were required to layout a linear feedback shift register circuit (LFSR) designed in another module which the students were taking in the same semester. The LFSR circuit (Figure 3) designed by the students differed slightly due to different pseudo-random numbers to be generated.

Figure 3. Linear Feedback Shift Register.

Each group is to complete the layout of the LFSR using the ECAD software which can be access on campus. The layout must have no design rule errors and is to be correctly connected. The layout should occupy minimum area and conform to the standard cell layout methodology.

The students have to collect, collaborate, construct and record their understanding of Digital IC layout methodologies in their wiki. They are to layout primitive logic cells and create a library of IC layout cells called a Standard Cell Library. They will then use the cell library created to the layout of the LFSR. Upon completion they will reflect on their work. The e-portfolio tool in the Blackboard suite is used by students to deposit their completed work and to record their reflections.

#### Implementation

Students in groups of 4-5 students work on the project over 6 weeks. There are deliverables at every stage of the project to monitor the students' progress and provide timely feedback.

The schedule is given to the students at the beginning of the term so that the students are aware of the deadlines. The schedule follows the sequence: (a) project clarification (b) investigation (c) processing of data (d) realization and (e) evaluation.

| Week no. | Objectives                                             | Resources/ Tools   |

|----------|--------------------------------------------------------|--------------------|

| 1        | To form groups. Ice-breaking.(#)                       |                    |

|          | Clarification of project specifications. (#)           | Blackboard™        |

|          | Learn how to use the e-learning platform.              |                    |

| 2        | Find information regarding a list of topics which will | Library            |

|          | be useful for their projects.                          | Web Search Engines |

|          | Identify knowledge gaps.                               |                    |

| 3        | Understand, organize and summarise the                 | Wiki               |

|          | information collected.                                 |                    |

|          | Share and review content information. (#)              |                    |

#### Table 2 Work Schedule

| 4 | Plan and design standard cell library.(#)<br>Apply the information to layout the primitive logic<br>cells.<br>Create the standard cell library.(#)                                                                                                                                                                                                                                                                                                                      | ECAD software |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 5 | To layout the LFSR using the cell library created by<br>the group.<br>To verify that the LFSR layout follows the design<br>rules and is connected correctly.                                                                                                                                                                                                                                                                                                            | ECAD software |

| 6 | Upload completed layout of logic cells and LFSR to<br>their e-portfolio.<br>Compares and contrasts the layout of the LFSR<br>done by each member of the team. Decide on<br>which LFSR layout is the best. (#)<br>Reflect on their LFSR layout and how it conforms<br>to the standard cell layout methodology. They are<br>also to reflect on how they could improve their<br>layout and the way they have carried out their work<br>so as to improve their productivity | e-portfolio   |

#### (#) – group work

The ice-breaking activity in the first week help the students form small learning communities and iron-out any technical problems due to unfamiliarity with the platform used or the on-line tools to be used in the e-activities that follows.

Students are guided in their collecting of information by a list of questions from the instructor. These open-ended questions ensure that the students do not stray too far from the topic, given the tight project schedule. They may inquire further into the questions arising from their answers.

The students construct their content knowledge in a wiki. Their group mates review and modify the content. The instructor is able to view the history of the amendments and note the contributions of the team members.

In week 4, the students apply their new knowledge of the Standard Cell Layout Methodology to the construction of a set of rules for their Standard Cell Library. Each student will create a layout a primitive logic gate based on the design rules and the rules they had created for their Standard Cell Library. The layout process will require students to plan, design and verify that the layout done is correct. The student must analyze the error reports and correct the layout. Only when their layout is error free can they proceed to layout the LFSR in week 5.

On completion, the student will upload their work to their e-portfolio. They reflect on their work vis-à-vis the Standard Cell Layout Methodology and their peers work.

#### Assessment

The structured project is given 20% weight in the module assessment. 65% of which is individual assessment and 35% of the marks for this activity is given for group work. 60% of the

mark is allocated for formative assessment and the remaining 40% for summative assessment. Table 3 shows a detailed breakdown of the marks allocated for each activity.

|                                          | Individual | Group | Total |

|------------------------------------------|------------|-------|-------|

| Ice Breaker                              | 5          |       | 5     |

| Content Creation                         | 20         | 5     | 25    |

| Planning                                 |            | 10    | 10    |

| Layout of Primitive Cell (*)             | 20         |       | 20    |

| Creation of Standard Cell<br>library (*) |            | 10    | 10    |

| Layout of LFSR (*)                       | 10         |       | 10    |

| Evaluation                               |            | 10    | 10    |

| Reflection                               | 10         |       | 10    |

| TOTAL                                    | 65         | 35    | 100   |

## Table 3 Allocation of marks

(\*) Summative Assessment

The rubrics used for the formative assessment is shown in Append A. The summative assessment is mainly obtained from the design rule check report and other reports generated by the ECAD tool.

## Evaluation

An indication of the effectiveness of the project-based method used can be extracted from the reflections of the students. Out of the class of 42 students, over 90% of the students indicated that they have learnt how to layout using the Standard Cell Methodology from the project. Besides the content knowledge, 33% appreciated the teamwork; 21% learnt the value of planning and 21% felt a sense of achievement and satisfaction upon completion of the project. The details of their feedback are shown in Table 4.

| Learning Areas                                  | % of class<br>agreeing that they<br>have benefited<br>from the project |

|-------------------------------------------------|------------------------------------------------------------------------|

| Technical Knowledge                             | 90%                                                                    |

| (Example: Learnt how to use Standard Cell       |                                                                        |

| Methodology from the project )                  |                                                                        |

| Personal and Professional Skills and Attributes |                                                                        |

| Teamwork                                        | 33%                                                                    |

| Sense of Achievement                            | 21%                                                                    |

| See Value in Planning                           | 21%                                                                    |

| Learnt/ Applied Problem Solving Skills          | 14%                                                                    |

| Time-Management                                 | 10%                                                                    |

Table 4 Data from Students' Reflection

Sample size: 42 students

Here is a sample of some of the students' reflections:

"I felt that this layout was one of the best I have done, because the amount of time and effort that I have put in were much more compared to the other assignments. I followed the design rules and guidelines while accomplishing this task. For example, not using long poly silicon lines to connect from one gate to another as it will result in signal skews."

"During this project, we discussed the problems together, helped each other and stayed back at school until it finished. This was very inspiration among us and I learnt how to communicate with each other."

"I was still thrilled with the first hands-on experience in my life in doing an IC layout. Most importantly in this mini-project, I learnt to appreciate the value of team-working in IC layouts as each person's job is equally important; regardless of how much weight his/her work carry."

"This DFF lab took about 2 weeks time for us to finish, I have to stay back every evening to catch up with my progress. It was really an exhausting period. On the day of submission, when I look at my work, I was full of satisfaction. From a person that do not know layout design to a person that can produce out the complicated DFF layout. It was a journey of growth,"

The results of summative assessment showed 100% of the students completed the layout of the primitive logic cells and the LFSR in the given time. Their layout conformed to the Standard Cell Methodology and met the design rules requirements. Their layouts passed the DRC and LVS verification checks performed by the ECAD tools.

It was observed that the students' successful experience in the structured project produced a more positive climate in the classroom thereafter. This may be because they were then able to relate the downstream lessons with their project experience.

## SUMMARY

By leveraging on the Web 2.0 tools, project-based learning is made more collaborative and allows the students to reach out to more resources than the campus can ever hold. It allows students to collaboratively construct online content and reflect on their learning.

The structured project was a suitable alternative method of delivering the topics in the Integrated Circuit Layout module that were "dry", rule-based rich content and too abstract for the students. The students are more motivated and willing to put in extra effort because of the engaging nature of project-based learning. The visible outcomes of their efforts give these students a sense of satisfaction and achievement. They achieve a better understanding by constructing the content themselves, monitor their progress and work together to achieve the desired outcome. While the content knowledge may become obsolete in future, the soft-skills that they learnt and experience in this project will help them in their lifelong learning journey.

#### REFERENCES

- 1. Kenneth Adderley et al, Project Methods in Higher Education, SHRE 1979

- 2. Jane Henry. Kogan, *Teaching through Projects*, Page 1994.

- 3. Robin Forgarty, Problem-based Learning and other Curriculum Models for the Multiple Intelligence Classroom. Pearson 1997.

- 4. Tanja Jadin et al. *Relevant aspects of successful project-based learning with Web 2.0 tools in schools*. Retrieved on April 10, 2009, from <u>http://www.slideshare.net/tjadin/relevant-aspects-of-successful-projectbased-learning-with-web-20-tools-in-schools-presentation</u>.

- 5. Christopher Saint, Judy Saint. IC mask design : essential layout techniques. McGraw-Hill, c2002.

- 6. Michael John Sebastian Smith. Application specific integrated circuits. Addison-Wesley, c1997.

- 7. Texas Instruments. What's an LFSR? Texas Instruments Incorporated 1996.

- 8. Learners Together article. *Teaching Integrated Circuits via Online Discussion.* http://www.learnerstogether.net/

#### **Biographical Information**

Linus Low is a lecturer in the division of Electronic and Computer Engineering at Ngee Ann Polytechnic (Singapore). He is the module leader for IC Layout module.

#### Corresponding author

Linus Low Koon Teck Ngee Ann Polytechnic School of Engineering Electronic & Computer Engineering Division 535, Clementi Road, Singapore 599489 Telephone: +65-64606397 Email: lkt1@np.edu.sg

## APPEND A

Rubric used for Formative Assessment

| Tasks<br>completion               | Level 1 (0-<br>30%)                                                        | Level 2 (30 to<br>60%)                                                                                                 | Level 2 (60 to<br>80%)                                                                                                                                           | Level 3 (80 to 100%)                                                                                                                                                              |

|-----------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ice Breaker                       | No participation                                                           | NA                                                                                                                     | Participated                                                                                                                                                     | participated well                                                                                                                                                                 |

| Content<br>Creation:<br>research  | Information that<br>lacked<br>relevance,<br>quality, depth<br>and balance. | information from a<br>limited range of<br>sources and<br>displayed minimal<br>effort in selecting<br>quality resources | information from<br>a variety of<br>relevant sources-<br>-print and<br>electronic                                                                                | <ol> <li>Information from a<br/>variety of quality<br/>electronic and print<br/>sources.</li> <li>Sources are relevant<br/>and balanced.</li> </ol>                               |

| Content<br>Creation:<br>synthesis | Not logically or<br>effectively<br>structured.                             | could have put<br>greater effort into<br>organizing the<br>content                                                     | logically<br>organized the<br>product and<br>made good<br>connections<br>among ideas                                                                             | <ol> <li>Developed appropriate<br/>structure for<br/>communicating content</li> <li>Information is logically<br/>and creatively organized<br/>with smooth transitions.</li> </ol> |

| Content<br>Creation :<br>citation | Clearly<br>plagiarized<br>materials.                                       | Need to use<br>greater care in<br>documenting<br>sources.                                                              | <ol> <li>Documented<br/>sources with<br/>some care</li> <li>Sources are<br/>cited.</li> <li>Few errors<br/>noted.</li> </ol>                                     | <ol> <li>Documented all<br/>sources.</li> <li>Sources are properly<br/>cited.</li> <li>No errors noted.</li> </ol>                                                                |

| Content<br>Creation (G)           | 1. Developed a<br>question<br>requiring little<br>creative<br>thought.     | 1. constructed a<br>question that lends<br>itself to readily<br>available answers                                      | 1. focused and<br>challenging<br>question                                                                                                                        | <ol> <li>Thoughtful, creative<br/>question</li> <li>breaks new ground or<br/>contributes to knowledge<br/>in a focused, specific<br/>area</li> </ol>                              |

| Planning (G)                      | 1. task divided<br>amongst<br>members                                      | 1. Task divided<br>amongst members<br>2. non-well defined<br>specifications for<br>standard cell<br>library            | <ol> <li>Task divided<br/>amongst<br/>members</li> <li>fairly-well<br/>defined but<br/>incorrect<br/>specifications for<br/>standard cell<br/>library</li> </ol> | <ol> <li>task divided amongst<br/>members</li> <li>well defined and correct<br/>specifications rules for<br/>standard cell library</li> </ol>                                     |

| Layout of<br>primitive cell<br>(I)          | 1. layout was<br>incomplete                                                                                     | 1. Layout was<br>completed<br>2. Layout cleared<br>Design Rule<br>Check                                                                                  | 1. Layout was<br>completed<br>2. Layout cleared<br>Design Rule<br>Check<br>3. Layout<br>corresponds with<br>schematic (LVS)                             | <ol> <li>Layout was completed</li> <li>Layout cleared Design<br/>Rule Check</li> <li>Layout corresponds<br/>with schematic (LVS)</li> <li>Layout is optimised for<br/>area and can be used in<br/>the cell library</li> <li>Layout was completed<br/>on time.</li> </ol> |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Creation of<br>Standard Cell<br>Library (G) | 1. No missing<br>layout cells in<br>the cell library                                                            | <ol> <li>No missing<br/>layout cells in the<br/>cell library</li> <li>Cell library<br/>corresponds does<br/>not meet the specs<br/>in part(4)</li> </ol> | <ol> <li>No missing<br/>layout cells in the<br/>cell library</li> <li>Cell library<br/>corresponds<br/>meets the specs<br/>in part(4)</li> </ol>        | <ol> <li>No missing layout cells<br/>in the cell library</li> <li>Cell library<br/>corresponds meets the<br/>specs in part(4)</li> <li>Cell library delivered<br/>on time.</li> </ol>                                                                                    |

| Layout of<br>LFSR (I)                       | 1. layout was<br>incomplete                                                                                     | 1. Layout was<br>completed<br>2. Layout cleared<br>Design Rule<br>Check                                                                                  | <ol> <li>Layout was<br/>completed</li> <li>Layout cleared<br/>Design Rule<br/>Check</li> <li>Layout<br/>corresponds with<br/>schematic (LVS)</li> </ol> | <ol> <li>Layout was completed</li> <li>Layout cleared Design<br/>Rule Check</li> <li>Layout corresponds<br/>with schematic (LVS)</li> <li>Layout is optimized for<br/>area and can be used in<br/>the cell library</li> <li>Layout was completed<br/>on time.</li> </ol> |

| Evaluation (G)                              | <ol> <li>Restating<br/>information.</li> <li>Conclusions<br/>were not<br/>supported by<br/>evidence.</li> </ol> | 1. Conclusions<br>could be<br>supported by<br>stronger evidence.<br>Level of analysis<br>could have been<br>deeper.                                      | 1. good effort<br>was made in<br>analyzing the<br>evidence<br>collected                                                                                 | 1. Analyzed the<br>information collected and<br>drew appropriate and<br>inventive conclusions<br>supported by evidence.                                                                                                                                                  |

| Reflection (I)                              | 1. Lackluster                                                                                                   | 1. Somewhat<br>superficial<br>consideration of<br>issues                                                                                                 | 1. Accurate<br>consideration of<br>issues                                                                                                               | 1. Excellent evaluation of the issues                                                                                                                                                                                                                                    |

(I) - individual

(G) – group work